Fail-Safe Storage with the TREEspan File System Part 2: TSFS Transactions

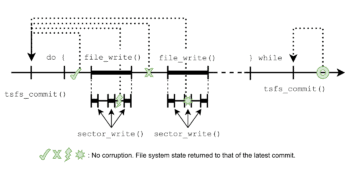

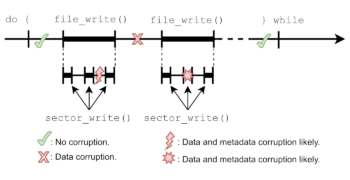

In this second article in this series we see how an application can be designed to withstand such unforeseen events, using TSFS transactions. Doing so, we introduce the tsfs_commit() API. We also discuss the write transaction atomicity property, by which applications can be safely designed ignoring potential partial update issues.