BASEplatform Bring-Up on the Toradex Colibri iMX7

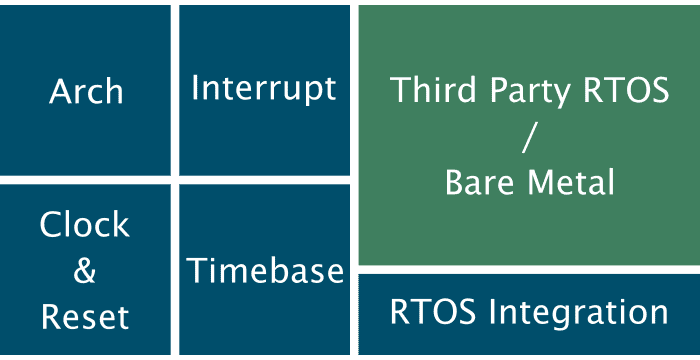

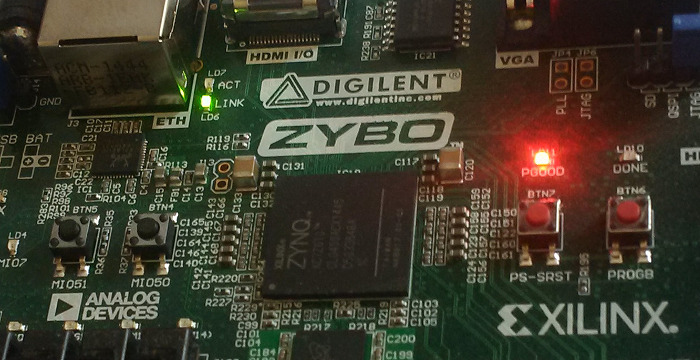

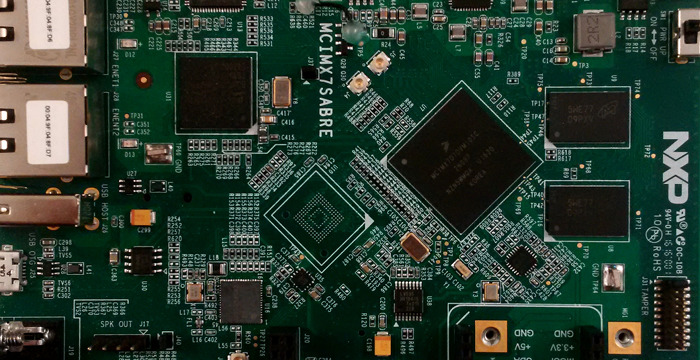

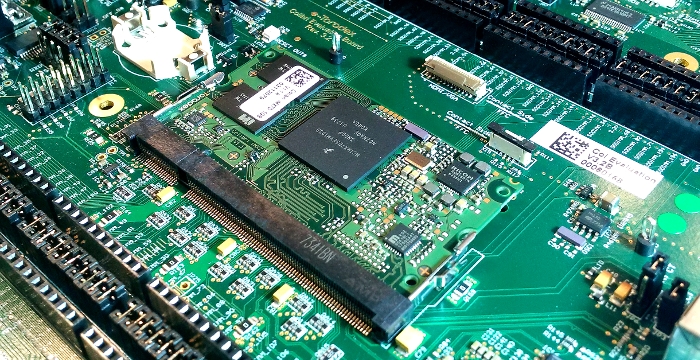

This article will go over some aspects of the early bring-up experience using the BASEplatform™ on the Toradex Colibri iMX7 System on Module (SoM). It will also cover features and advantages of the Colibri SoM for embedded developers interested in using an RTOS or a bare-metal environment on the NXP i.MX7 SoC. The BASEplatform is