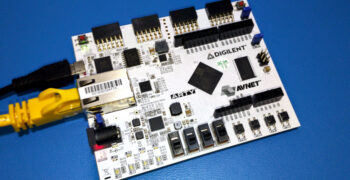

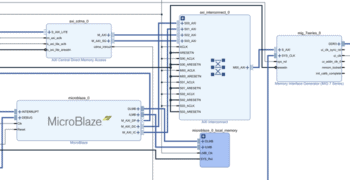

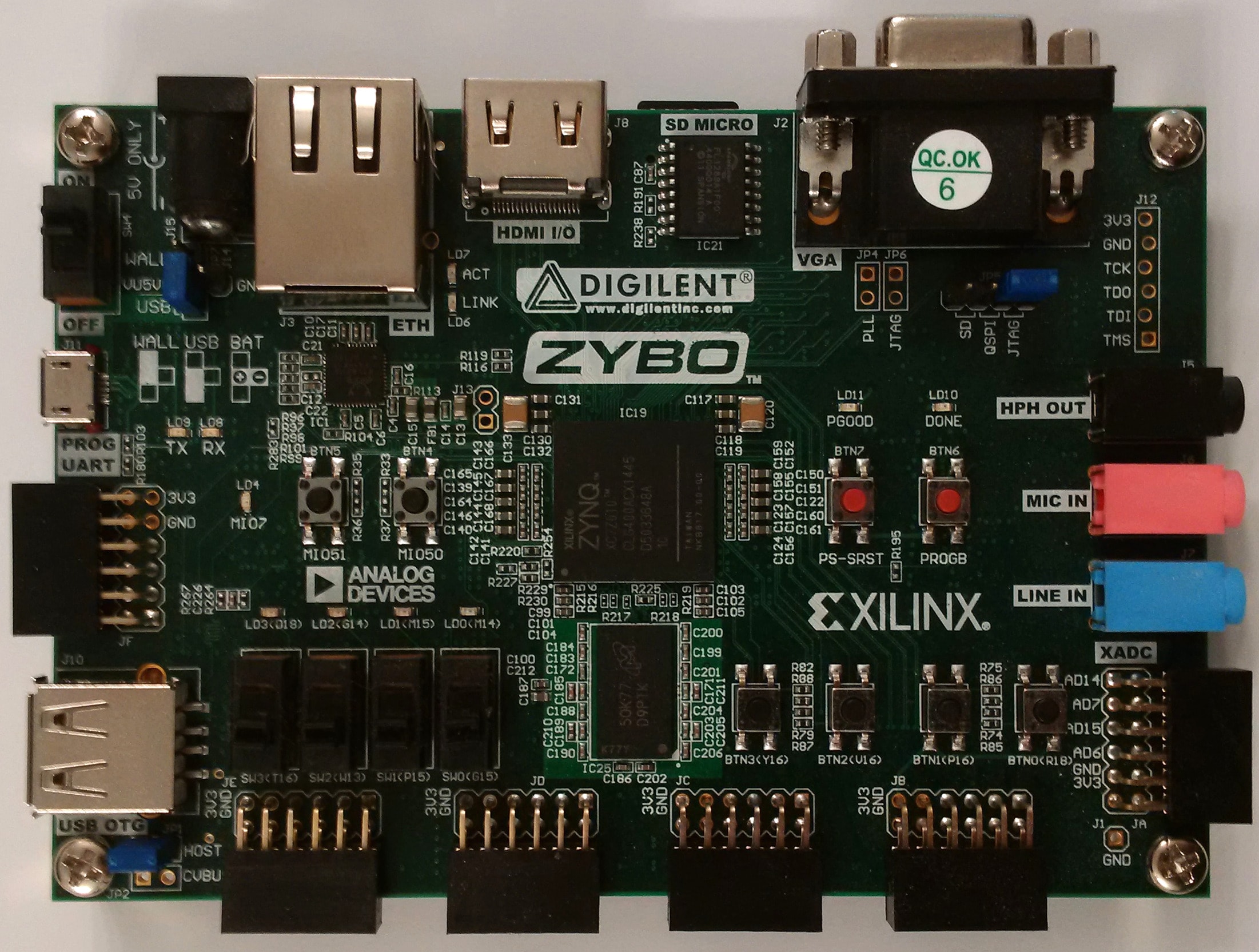

In two previous articles, I have looked at using Micrium’s uC/OS RTOS on the Xilinx Zynq-7000. I only covered kernel and storage. This time, I will be exploring some connectivity options in combination with the Digilent Zybo. Namely, using Micrium’s USB device solution and HTTP server through the Zybo’s Ethernet port. This is also a perfect opportunity to try the new and improved release of Vivado 2017.1.

The plan is to use the Zybo on-board SD Card to hold the html files for the HTTP server. To make it more interesting, instead of just copying the files using a PC, I’ll turn the Zybo into a USB mass storage device to access the SD Card.