Continuing from the last post, this article explores features specific to early members of the ARM Cortex-A family such as the Cortex-A9 which can help reduce interrupt latency. Namely the L2 cache and TLB lockdown features found in those processors. It’s important to note that those two features are not available in more recent 32 and 64 bits ARM processors such as the Cortex-A7. Newer cores have a simpler TLB, and most often than not an integrated L2 cache instead of the external L2 found on the A9. However, the Cortex-A9 is still a popular core, found on the Xilinx Zynq-7000 and NXP i.MX 6 SoCs to name a few.

Estimating Worst Case Interrupt Latency at Runtime

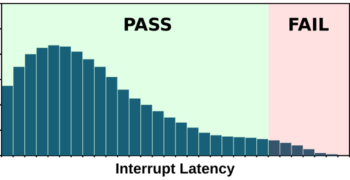

This article shows a simple way of estimating worst case interrupt latency at runtime which can be implemented on most MCUs and RTOSes or even bare-metal. All that is needed is a hardware timer that can generate an interrupt after an arbitrary time delay. The technique is also rather non-intrusive, making it usable all the way to production without significantly affecting the application’s performance.