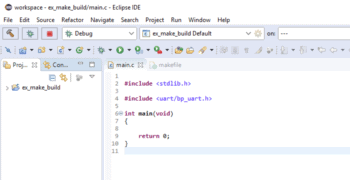

GCC Toolchain Eclipse Setup Guide Part 1 — Eclipse and GCC

In part 1 of this series is a complete step-by-step installation and configuration guide for all the tools required to integrate a GCC toolchain within the Eclipse IDE. Including obviously Eclipse and your selected GCC toolchain as well as the MSYS2 UNIX environment for Windows.